未命名

2023-12-12

第四章 总线驱动与控制

74LS245 双向数据总线

- DIR = 1:\(A\to B\)

- \(E\) 为 1时,AB均为高阻,实现总线隔离

74LS244 单向总线驱动

第5章 存储器设计

内存芯片

- SRAM:Static Random Access Memory静态随机读写存储器

- 异步型

- 6264:8K×8bit

- A0~A12:决定存储单元的容量,一般 1K~256M → 地址总线数:10~28

- D0~D7

- CS1、CS2

- OE 输出允许 (读)

- WE 写允许

- 6264:8K×8bit

- 同步型

- 异步型

ROM

EPROM:紫外线可擦除只读存储器

- 2764

EEPROM:电可擦除只读存储器

FLASH:闪速存储器

- NOR 型:写入擦除速度慢,有独立地址线、数据线,能随机访问,用于存储固件代码

- NAND 型:有更快的写入和擦除速度,顺序访问速度快,随机访问速度慢,用于存储卡

存储器设计

位扩展、字扩展

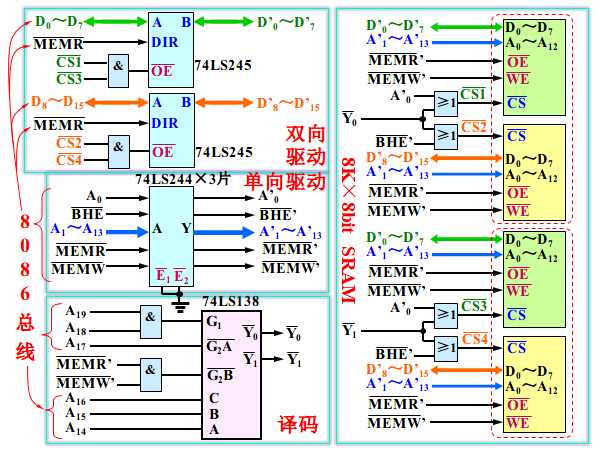

现有容量为 8K×8bit 的 SRAM 芯片。在8086系统中,

(1)利用这样的芯片构成地址范围为C0000H~C7FFFH的内存,画出最大模式下包括总线驱动在内的此芯片与系统总线的连接图(译码器件自行选择)。

(2)试编写8086汇编语言程序,从地址C0000H开始,依次写入数据,直到地址C7FFFH。要求数据从0开始,每写入一个字节后数据加1,即写入数据依次为:00H、01H、02H、03H、……、FEH、FFH、 00H、01H、……。然后逐个单元读出比较,若有错,则在DL中写入01H,退出检测;若每个单元均对,则在DL写入00H。

【解】

C8000H-C0000H=8000H,即32K,则:需要芯片片数=32KB/8KB=4片。

SRAM芯片 地址线:A0~A12 ,数据线:D0~D7

mark

mark

mark